# 20. Схема АЦП (Аналогово-цифровой преобразователь)

## объяснение на руссоком

https://www.youtube.com/watch?v=ncA_T1s2iYc

### Конспект (в процессе)

Преобразователь аналога в цифры

Бывает нескольких типов

Например АЦП слежения

Если частота выше - поднять на 1. Если ниже - опустить на 1. Хорошо работает с небольшими изменениями, плохо с крутыми. Организация архитектуры простая, время быстрое

В авр используется АЦП последовательного приближения: подразрядного уравновешивания. Всего 4 бита.

Ставим все в 0.пытаемся первый бит выставить в 0.

Смотрим, выше ли наш сигнал входного. Если выше - ставим 0. Если ниже - ставим 1.

Проделываем то же самое с каждым битом слева направо

(Внимание, инвертировано. 0000 это 8h, 1111 = 0h)

С увеличением количества бит скорость растёт линейно, а точность экспоненциальнл

Для крутых изменений подходит хорошо. Не долго по времени. Довольно точно

[Основной источник: microsin.net](http://microsin.net/programming/avr/atmega16-adc.html)

Аналого-цифровой преобразователь — устройство, преобразующее входной аналоговый сигнал в дискретный код (цифровой), как правило - преобразующее **напряжение в двоичный цифровой код**

### Аналоговый и цифровой сигналы

> [name=Дарья Воронская] Имхо, лучше это заботать, так как вопрос - а че такое аналог и цифра от непредсказуемого препода - вполне... предсказуемо?

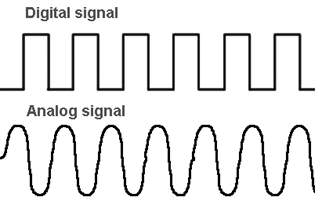

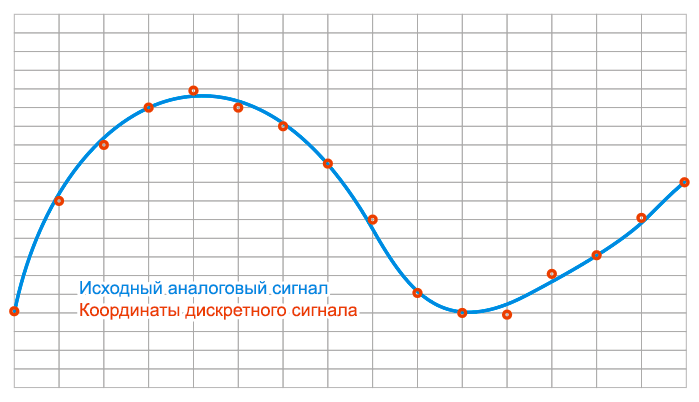

**Сигнал аналоговый** - это сигнал непрерывный, имеющий бесконечное число **близких по значению** данных в пределах максмальных, все параметры которого описываются временной зависимой переменной.

** Сигнал цифровой** – это раздельный сигнал, описываемый **раздельной функцией времени**, соответственно в каждый момент времени, величина амплитуды сигнала имеет строго определенное значение. У цифрового сигнала координаты по горизонтальной оси расположены через равные промежутки времени, в соответствии с частотой дискретизации.

отличия аналогового и цифрового сигнала состоят:

- В непрерывности аналогового и дискретности цифрового;

- В большей вероятности помех при передаче аналогового;

- В избыточности аналогового сигнала;

- В способности цифрового фильтровать помехи и восстанавливать исходую информацию;

- В передаче цифрового сигнала в закодированной форме. Один аналоговый сигнал замещается несколькими цифровыми.

## Cхема АЦП на английском

## Cхема АЦП на русском

## Перевод информации из datasheet

:::spoiler Оригинал на английском

The ADC converts an analog input voltage to a 10-bit digital value through successive approximation. The minimum value represents GND and the maximum value represents the voltage on the AREF pin minus 1 LSB. Optionally, AVCC or an internal 2.56V reference voltage may be connected to the AREF pin by writing to the REFSn bits in the ADMUX Register. The internal voltage reference may thus be decoupled by an external capacitor at the AREF pin to improve noise immunity.

The analog input channel and differential gain are selected by writing to the MUX bits in ADMUX. Any of the ADC input pins, as well as GND and a fixed bandgap voltage reference, can be selected as single ended inputs to the ADC. A selection of ADC input pins can be selected as positive and negative inputs to the differential gain amplifier.

If differential channels are selected, the differential gain stage amplifies the voltage difference between the selected input channel pair by the selected gain factor. This amplified value then becomes the analog input to the ADC. If single ended channels are used, the gain amplifier is bypassed altogether.

The ADC is enabled by setting the ADC Enable bit, ADEN in ADCSRA. Voltage reference and input channel selections will not go into effect until ADEN is set. The ADC does not consume power when ADEN is cleared, so it is recommended to switch off the ADC before entering power

saving sleep modes.

The ADC generates a 10-bit result which is presented in the ADC Data Registers, ADCH and ADCL. By default, the result is presented right adjusted, but can optionally be presented left adjusted by setting the ADLAR bit in ADMUX.

If the result is left adjusted and no more than 8-bit precision is required, it is sufficient to read ADCH. Otherwise, ADCL must be read first, then ADCH, to ensure that the content of the Data Registers belongs to the same conversion. Once ADCL is read, ADC access to Data Registers is blocked. This means that if ADCL has been read, and a conversion completes before ADCH is

read, neither register is updated and the result from the conversion is lost. When ADCH is read, ADC access to the ADCH and ADCL Registers is re-enabled.

The ADC has its own interrupt which can be triggered when a conversion completes. When ADC access to the Data Registers is prohibited between reading of ADCH and ADCL, the interrupt will trigger even if the result is lost.

:::

## Принцип действия

АЦП преобразовывает входное аналоговое напряжение в 10-разр. методом последовательных приближений. Минимальное значение соответствует уровню GND, а максимальное уровню AREF минус 1 мл. разр. К выводу AREF опционально может быть подключено напряжение AVCC или внутренний ИОН на 1.22В путем записи соответствующих значений в биты REFSn в регистр ADMUX. Несмотря на то, что ИОН на 2.56В находится внутри микроконтроллера, к его выходу может быть подключен блокировочный конденсатор для снижения чувствительности к шумам, т.к. он связан с выводом AREF.

Канал аналогового ввода и каскад дифференциального усиления выбираются путем записи бит MUX в регистр ADMUX. В качестве однополярного аналогового входа АЦП может быть выбран один из входов ADC0…ADC7, а также GND и выход фиксированного источника опорного напряжения 1,22 В. В режиме дифференциального ввода предусмотрена возможность выбора инвертирующих и неинвертирующих входов к дифференциальному усилителю.

Если выбран дифференциальный режим аналогового ввода, то дифференциальный усилитель будет усиливать разность напряжений между выбранной парой входов на заданный коэффициент усиления. Усиленное таким образом значение поступает на аналоговый вход АЦП. Если выбирается однополярный режим аналогового ввода, то каскад усиления пропускается

Работа АЦП разрешается путем установки бита ADEN в ADCSRA. Выбор опорного источника и канала преобразования не возможно выполнить до установки ADEN. Если ADEN = 0, то АЦП не потребляет ток, поэтому, при переводе в экономичные режимы сна рекомендуется предварительно отключить АЦП.

АЦП генерирует 10-разрядный результат, который помещается в пару регистров данных АЦП ADCH и ADCL. По умолчанию результат преобразования размещается в младших 10-ти разрядах 16-разр. слова (выравнивание справа), но может быть опционально размещен в старших 10-ти разрядах (выравнивание слева) путем установки бита ADLAR в регистре ADMUX.

Практическая полезность представления результата с выравниванием слева существует, когда достаточно 8-разрядное разрешение, т.к. в этом случае необходимо считать только регистр ADCH. В другом же случае необходимо первым считать содержимое регистра ADCL, а затем ADCH, чем гарантируется, что оба байта являются результатом одного и того же преобразования. Как только выполнено чтение ADCL блокируется доступ к регистрам данных со стороны АЦП. Это означает, что если считан ADCL и преобразование завершается перед чтением регистра ADCH, то ни один из регистров не может модифицироваться и результат преобразования теряется. После чтения ADCH доступ к регистрам ADCH и ADCL со стороны АЦП снова разрешается.

**АЦП генерирует собственный запрос на прерывание** по завершении преобразования. Если между чтением регистров ADCH и ADCL запрещен доступ к данным для АЦП, то прерывание возникнет, даже если результат преобразования будет потерян.

## Запуск преобразования

Одиночное преобразование запускается путем записи 1 в бит ADC ADSC (регистр ADCSRA). Данный бит сбрасывается по завершении преобразования. Если в процессе преобразования переключается канал аналогового ввода, то ADC автоматически завершит текущее преобразование прежде, чем переключит канал.

Другой вариант запуска преобразования – автоматический запуск по сигналу из различных источников. В режиме автоматического перезапуска ADC непрерывно оцифровывает аналоговый сигнал и обновляет регистр данных ADC. Данный режим задается путем записи 1 в бит ADATE регистра ADCSRA.

Можно также выбрать источник перезапуска битами ADTS регистра SFIOR. Когда происходит положительный перепад выбранного сигнала перезапуска, сбрасывается прескалер ADC и запускается преобразование. Это предоставляет метод запуска преобразования в фиксированные интервалы времени. Если сигнал запуска все еще установлен, когда преобразование завершено, новое преобразование не запускается. Если происходит положительный перепад выбранного сигнала перезапуска происходит во время преобразования, этот перепад будет игнорирован.

Внимание – флаг прерывания ADIF будет все равно установлен, даже если соответствующее прерывание запрещено или бит I (глобальные прерывания) регистра [SREG](/BhJ3OyD_RIi3lcawKRJbyg) сброшен, при этом преобразование запустится без генерации прерывания. Однако флаг прерывания ADIF должен быть очищен, чтобы запустилось новое преобразование при следующем событии прерывания.

Использование флага прерывания ADC (ADIF) как источника запуска преобразования запускает новое преобразование, как только текущее преобразование завершается. Таким образом, ADC работает в режиме автозапуска - непрерывно оцифровывает аналоговый сигнал и обновляет регистр данных ADC. Первое преобразование инициируется путем записи 1 в бит ADSC регистра ADCSRA. В данном режиме ADC выполняет последовательные преобразования, независимо от того - сброшен флаг прерывания ADC ADIF или нет.

Если разрешен автозапуск (установлен бит ADATE регистра ADCSRA), одиночные преобразования могут запускаться путем записи лог. 1 в бит ADSC регистра ADCSRA. Бит ADSC может использоваться для определения, происходит или нет в настоящий момент преобразование. Бит ADSC будет читаться как 1 во время выполнения преобразования, независимо от того, как оно было запущено.